AMD szykuje nam spore trzęsienie ziemi w świecie mikroarchitektury. Choć procesory Zen 5 weszy na rynek zaledwie rok temu, plotki o ich następcy, Zen 6, stają się coraz gorętsze. I tym razem nie mówimy tylko o kosmetycznym zwiększeniu taktowań, ale o fundamentalnej zmianie w sposobie komunikacji rdzeni.

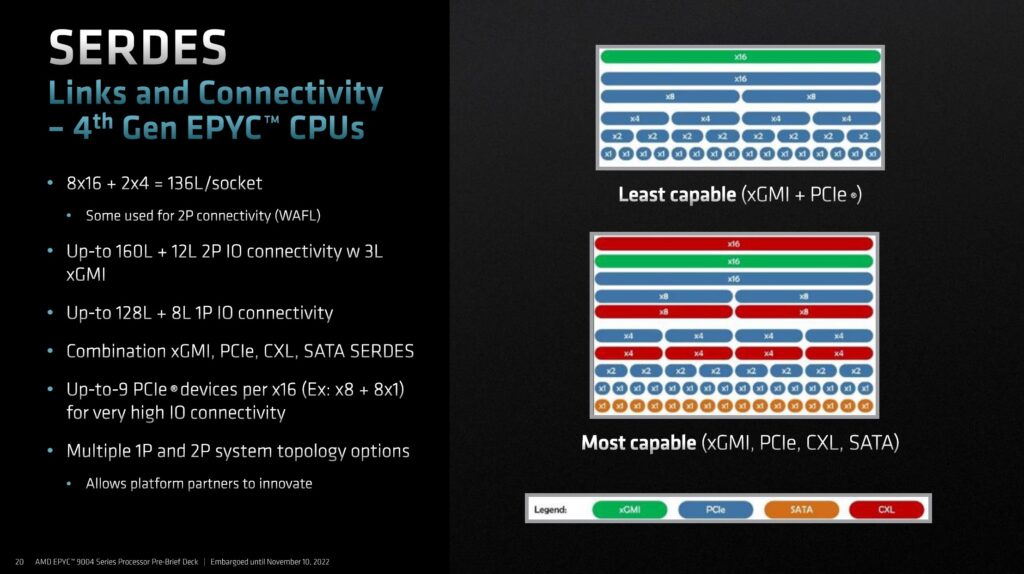

Jak donosi YouTuber @High Yield, AMD zamierza całkowicie porzucić stary system połączeń D2D (Die-to-Die) oparty na technologii SERDES (Serializer/Deserializer), który służył im wiernie od czasów Zen 2. Zamiast tego, w Zen 6 zobaczymy nowatorskie rozwiązanie, które już teraz przeszło chrzest bojowy w mobilnych układach Strix Halo APU. Co to dla nas oznacza? Drastyczne obniżenie opóźnień i znaczący skok efektywności energetycznej.

Czemu AMD ma już dość SERDES?

Dla tych z Was, którzy cenią sobie szybkość, musicie wiedzieć, że obecne procesory AMD (od Zen 2 w górę) używają SERDES, aby chiplety (CCD) mogły rozmawiać z układem I/O (IOD) na jednym kawałku krzemu. SERDES działa trochę jak kurier, który musi spakować duży ładunek w jedną, długą paczkę, wysłać ją, a odbiorca musi ją następnie rozpakować i złożyć z powrotem.

Technicznie rzecz biorąc, SERDES bierze równoległe dane i zamienia je na szybki szeregowy strumień bitów, by przesłać je przez interfejs, a następnie na końcu ten proces odwraca. I choć SERDES jest niezbędny przy komunikacji na większe odległości (np. pomiędzy oddzielnymi komponentami), wewnątrz opakowania procesora (package) generuje dwa poważne problemy:

- Zapotrzebowanie energetyczne: Ciągłe serializowanie i deserializowanie, wraz z potrzebą synchronizacji zegara, marnuje cenną energię.

- Opóźnienie (Latency): Konwersja danych wprowadza dodatkowy czas oczekiwania. W czasach, gdy procesory mają na pokładzie coraz więcej specjalistycznych jednostek (jak np. NPU do AI), potrzebujemy natychmiastowej i szerokiej komunikacji, a nie wąskiej, wolnej autostrady.

Nadchodzi „Sea-of-Wires”

Rozwiązanie, które AMD testuje w Strix Halo i planuje zaimplementować w Zen 6, jest tak eleganckie, jak to tylko możliwe. Zamiast kuriera pakującego dane, AMD stawia na metodę „Morza Kabli” (Sea-of-Wires).

Dzięki zaawansowanym technikom pakowania TSMC, takim jak InFO-oS (Fan-Out on Substrate) oraz RDL (Redistribution Layer), inżynierowie AMD mogą połączyć chiplety bezpośrednio za pomocą ogromnej liczby cienkich, równoległych przewodów biegnących przez podłoże.

Zapomnijcie o starym SERDES. Nowa architektura usuwa całe te moduły, zastępując je prostymi macierzami mikro-padów. Dane nie muszą być już pakowane i rozpakowywane. Zamiast czekać w kolejce na jednopasmowej drodze, dane mogą ruszać równocześnie, setkami pasów. Efekt? Znacznie szerszy kanał komunikacji przy niższym zużyciu energii i, co najważniejsze dla wydajności, z minimalnym opóźnieniem.

Oczywiście, ten rewolucyjny design ma swoje wady. Wdrożenie wielu warstw RDL jest skomplikowane i kosztowne, a cała przestrzeń na spodzie chipletów musi być teraz przeznaczona na te gęste połączenia. Jednak korzyści dla użytkowników końcowych są nie do przecenienia. Jeśli plotki się potwierdzą, Zen 6, który ma być produkowany w zaawansowanym procesie N3P od TSMC, otrzyma nie tylko lepsze rdzenie, ale i system komunikacji, który jest stworzony dla ery ultrawydajnych chipletów. Możemy oczekiwać, że równowaga między mocą a efektywnością energetyczną w Zen 6 przesunie się znacznie na korzyść AMD.